現(xiàn)貨庫存,2小時(shí)發(fā)貨,提供寄樣和解決方案

熱搜關(guān)鍵詞:

在高精度模擬信號(hào)采集系統(tǒng)中,模數(shù)轉(zhuǎn)換器(ADC)的采樣過程會(huì)引入混疊、量化噪聲和電容反沖等問題。傳統(tǒng)解決方案通常依賴外部抗混疊濾波器和驅(qū)動(dòng)放大器來緩解這些問題,但隨之而來的復(fù)雜性、功耗增加以及相位失配問題又成為新的挑戰(zhàn)。

本文將介紹連續(xù)時(shí)間Σ-Δ(CTSD)ADC架構(gòu),探討其如何通過內(nèi)在特性解決上述問題,從而簡化信號(hào)鏈設(shè)計(jì)、減少元件數(shù)量,并提升系統(tǒng)的整體性能與可靠性。

ADC的采樣過程包括兩個(gè)核心步驟:時(shí)域離散化(采樣) 和 幅值離散化(量化)。根據(jù)奈奎斯特采樣定理,采樣頻率必須至少為輸入信號(hào)最高頻率的兩倍,否則會(huì)出現(xiàn)頻譜混疊,導(dǎo)致信號(hào)失真。

此外,量化過程會(huì)引入量化噪聲,分布在奈奎斯特帶寬內(nèi)。為抑制混疊和降低量化噪聲影響,通常采用以下方法:

使用高階抗混疊濾波器(AAF)

引入過采樣技術(shù)

結(jié)合噪聲整形

對(duì)于傳統(tǒng)的逐次逼近寄存器(SAR)ADC和離散時(shí)間Σ-Δ(DTSD)ADC,這些措施雖有效,但也帶來了顯著的設(shè)計(jì)負(fù)擔(dān),尤其是在中等帶寬、多通道或精密測(cè)量場(chǎng)景中。

CTSD ADC 是 Σ-Δ ADC 的一種變體,其核心區(qū)別在于采樣點(diǎn)位于反饋環(huán)路中的量化器之后,而非輸入端。這一結(jié)構(gòu)帶來以下關(guān)鍵優(yōu)勢(shì):

固有混疊抑制能力

輸入信號(hào)在進(jìn)入量化器前先經(jīng)過環(huán)路濾波器處理,使得任何折返到帶內(nèi)的混疊信號(hào)也受到相同濾波器的影響。因此,無需使用外部抗混疊濾波器即可實(shí)現(xiàn)優(yōu)異的混疊抑制效果。

阻性輸入特性

CTSD ADC 的輸入呈現(xiàn)為純阻性負(fù)載,消除了開關(guān)電容結(jié)構(gòu)帶來的電容反沖和建立時(shí)間問題,從而省去輸入驅(qū)動(dòng)放大器的需求。

恒定基準(zhǔn)輸入阻抗

基準(zhǔn)輸入同樣為阻性,避免了傳統(tǒng)ADC中因開關(guān)動(dòng)作引起的瞬態(tài)電流波動(dòng),無需額外緩沖器,進(jìn)一步簡化設(shè)計(jì)。

低延遲信號(hào)鏈

因無需外部濾波器,整體信號(hào)路徑更短,延遲更低,適用于對(duì)實(shí)時(shí)性要求較高的閉環(huán)控制和高速數(shù)據(jù)采集系統(tǒng)。

出色的多通道相位匹配性能

多個(gè)CTSD ADC并行使用時(shí),由于不存在復(fù)雜的外部濾波器,各通道間的相位誤差大大減小,非常適合振動(dòng)監(jiān)測(cè)、聲吶、電力測(cè)量等應(yīng)用。

| 特性 | SAR ADC | DTSD ADC | CTSD ADC |

|---|---|---|---|

| 抗混疊濾波器需求 | 高階濾波器(5階以上) | 中階濾波器(2~3階) | 無 |

| 輸入結(jié)構(gòu) | 開關(guān)電容 | 開關(guān)電容 | 阻性 |

| 反沖問題 | 存在,需驅(qū)動(dòng)器 | 存在,需驅(qū)動(dòng)器 | 無 |

| 相位匹配 | 差 | 一般 | 優(yōu)秀 |

| 功耗 | 適中 | 較高 | 低 |

| 設(shè)計(jì)復(fù)雜度 | 高 | 中 | 低 |

從表中可見,CTSD ADC 在多個(gè)維度上優(yōu)于傳統(tǒng)架構(gòu),尤其適合需要高精度、低延遲和緊湊布局的應(yīng)用場(chǎng)景。

ADI 推出的 AD7134 是一款支持直流至 400 kHz 輸入帶寬的高精度 CTSD ADC,具備以下關(guān)鍵特性:

集成異步采樣率轉(zhuǎn)換器(ASRC),支持靈活輸出速率配置

支持多種工業(yè)標(biāo)準(zhǔn)接口(如 SPI)

提供高達(dá) 24 位分辨率和 100 dB SNR

內(nèi)部集成低漂移參考源和溫度傳感器

支持單電源供電,簡化電源管理

該器件特別適用于高密度多通道系統(tǒng),如測(cè)試測(cè)量設(shè)備、工業(yè)自動(dòng)化儀表、振動(dòng)分析儀等。

如需AD7134產(chǎn)品規(guī)格書、樣片測(cè)試、采購、BOM配單等需求,請(qǐng)加客服微信:13310830171。

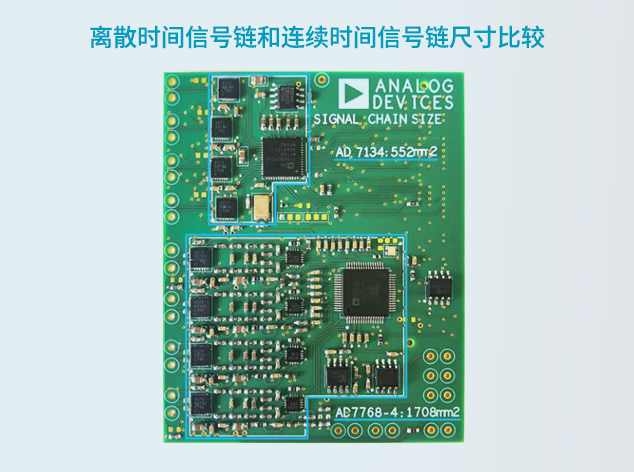

圖1和圖2展示了使用 CTSD ADC(如 AD7134)與傳統(tǒng) DTSD 架構(gòu)的信號(hào)鏈?zhǔn)疽鈭D和尺寸對(duì)比。結(jié)果顯示,在相同性能條件下,CTSD 方案可節(jié)省約70%的PCB空間,同時(shí)省去了抗混疊濾波器、驅(qū)動(dòng)放大器和基準(zhǔn)緩沖器等組件。

圖1

圖2

這種簡化不僅降低了物料成本(BOM),還提升了系統(tǒng)可靠性和生產(chǎn)一致性,加快產(chǎn)品上市進(jìn)程。

隨著工業(yè)自動(dòng)化、智能檢測(cè)和高精度測(cè)量需求的增長,傳統(tǒng)ADC架構(gòu)面臨的瓶頸日益凸顯。CTSD ADC 憑借其固有的混疊抑制、阻性輸入結(jié)構(gòu)、低延遲和高集成度,成為應(yīng)對(duì)中等帶寬、高精度應(yīng)用的理想選擇。

特別是像 AD7134 這類新型高性能 CTSD ADC 的推出,標(biāo)志著精密信號(hào)鏈設(shè)計(jì)正邁向更高效、更簡潔的新階段。對(duì)于工程師而言,這不僅意味著更低的設(shè)計(jì)門檻,也為系統(tǒng)優(yōu)化提供了更多可能性。