現(xiàn)貨庫存,2小時發(fā)貨,提供寄樣和解決方案

熱搜關(guān)鍵詞:

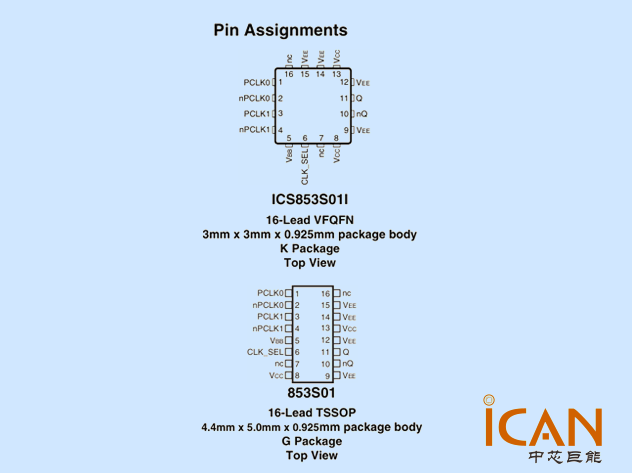

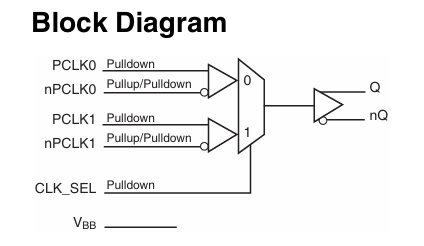

853S01 是瑞薩電子一款專為此類需求優(yōu)化的 2:1 差分至LVPECL多路復(fù)用器,兼具高速性能、電平兼容性與緊湊封裝,適用于空間受限的高密度PCB設(shè)計。瑞薩電子代理商-中芯巨能為您提供853S01 :中文技術(shù)參數(shù)詳解、引腳圖、原理圖及訂購料號。

核心功能與電氣特性

853S01提供兩個可選的差分輸入通道(PCLK0/nPCLK0 和 PCLK1/nPCLK1),支持 LVPECL 與 LVDS 電平直接接入,無需額外電平轉(zhuǎn)換電路。其單路LVPECL差分輸出對可驅(qū)動標(biāo)準(zhǔn)50Ω傳輸線,確保信號完整性。關(guān)鍵時序參數(shù)如下:

最大傳播延遲:490 ps(從輸入到輸出)

通道間偏斜(Part-to-part skew):≤150 ps(最大值)

工作電壓:支持 2.5V 或 3.3V 單電源供電,便于與不同邏輯域集成

工作溫度范圍:–40°C 至 +85°C,滿足工業(yè)級應(yīng)用要求

值得注意的是,該器件還支持通過外部電阻偏置網(wǎng)絡(luò),將 LVCMOS/LVTTL 單端信號轉(zhuǎn)換為偽差分輸入,從而擴(kuò)展其在混合信號系統(tǒng)中的適用性。具體方法是在nPCLKx引腳通過電阻連接至參考電壓(如VCC/2),而PCLKx接收單端時鐘,形成人工差分對。

冗余時鐘切換:在通信設(shè)備中,主備時鐘源通過853S01實現(xiàn)無縫切換,保障系統(tǒng)連續(xù)運行;

測試平臺多源激勵:ATE系統(tǒng)利用其低偏斜特性,在不同參考時鐘間快速切換,提升測試覆蓋率;

FPGA/ASIC時鐘前端:將來自不同PHY或收發(fā)器的LVDS/LVPECL時鐘統(tǒng)一轉(zhuǎn)換為LVPECL格式,供時鐘管理單元處理。

853S011BMILFT

853S011BGILF

853S011BGILFT

853S014AGILFT

853S01AGILFT

853S012AKILFT

853S012AKILF

853S01AGILF

853S011BMILF

853S014AGILF

853S011CGILF

853S011CGILFT

853S011CMILF

853S011CMILFT

853S01AKILF

瑞薩電子代理商-深圳市中芯巨能電子有限公司現(xiàn)貨供應(yīng),一片起訂,滿足您從研發(fā)到批量生產(chǎn)的所有大小批量采購需求。為制造業(yè)廠家的工程師或采購提供選型指導(dǎo)+數(shù)據(jù)手冊+樣片測試+技術(shù)支持等服務(wù)。如需產(chǎn)品規(guī)格書、樣片測試、采購、技術(shù)支持等需求,請加客服微信:13310830171。