16年IC行業(yè)代理分銷(xiāo) 覆蓋全球300+品牌

現(xiàn)貨庫(kù)存,2小時(shí)發(fā)貨,提供寄樣和解決方案

24小時(shí)服務(wù)熱線: 0755-82539998

現(xiàn)貨庫(kù)存,2小時(shí)發(fā)貨,提供寄樣和解決方案

熱搜關(guān)鍵詞:

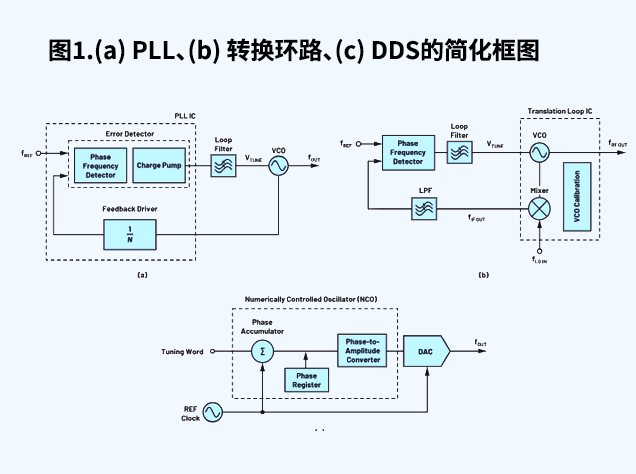

在射頻與高速數(shù)字系統(tǒng)設(shè)計(jì)中,頻率產(chǎn)生器件的選型直接影響系統(tǒng)相位噪聲、頻率捷變性、時(shí)鐘抖動(dòng)及整體性能。本文從關(guān)鍵性能指標(biāo)出發(fā),對(duì)比晶體振蕩器(XO)、壓控振蕩器(VCO)、鎖相環(huán)(PLL)頻率合成器、轉(zhuǎn)換環(huán)路(Offset PLL)及直接數(shù)字頻率合成器(DDS)五類(lèi)主流方案,幫助工程師快速匹配應(yīng)用場(chǎng)景。

選型首要考慮輸出頻率范圍,但需注意:寬帶或高頻能力往往以犧牲穩(wěn)定性、頻譜純度或切換速度為代價(jià)。

頻率穩(wěn)定性:短期穩(wěn)定性由相位噪聲(頻域)和相位抖動(dòng)(時(shí)域)表征;長(zhǎng)期穩(wěn)定性則體現(xiàn)為溫漂、老化引起的頻率偏移(單位:ppm)。

頻譜純度:關(guān)注諧波抑制比、雜散(spurs)及載波饋通水平,通常以dBc為單位。

開(kāi)關(guān)速度(建立時(shí)間):從指令發(fā)出到輸出頻率穩(wěn)定所需時(shí)間,對(duì)跳頻通信、快速掃描儀器至關(guān)重要。

晶體振蕩器(XO/VCXO):基于高Q值石英諧振器(Q > 10?),輸出頻率固定(kHz~數(shù)百M(fèi)Hz),相位噪聲極低(<-150 dBc/Hz @ 10 kHz偏移),長(zhǎng)期穩(wěn)定性可達(dá)±10 ppm。VCXO支持微調(diào)(±100 ppm量級(jí)),適用于需高穩(wěn)參考時(shí)鐘的場(chǎng)景,如基站時(shí)鐘、ADC/DAC采樣時(shí)鐘。缺點(diǎn)是頻率不可大范圍調(diào)節(jié)。

壓控振蕩器(VCO):采用LC諧振腔,Q值較低(~100),但支持GHz級(jí)輸出與寬調(diào)諧范圍(常達(dá)2:1以上)。單核高Q VCO相噪性能好但帶寬窄;多頻段切換式VCO通過(guò)切換諧振器實(shí)現(xiàn)寬帶覆蓋,但切換速度慢(μs級(jí))。VCO本身頻率漂移大,必須與PLL配合使用以鎖定頻率。

集成PLL頻率合成器(含VCO):將PLL鑒相器、電荷泵、分頻器與VCO集成于單芯片,僅需外接參考晶振與環(huán)路濾波器。支持?jǐn)?shù)字編程,頻率覆蓋可達(dá)數(shù)個(gè)倍頻程(如3 GHz–6 GHz),典型鎖定時(shí)間10–100 μs。適用于5G小基站、雷達(dá)本振等需靈活頻率配置的系統(tǒng)。相噪性能取決于VCO質(zhì)量與環(huán)路帶寬設(shè)計(jì)。

轉(zhuǎn)換環(huán)路(Offset PLL):用混頻器替代傳統(tǒng)分頻器,環(huán)路增益為1,顯著抑制帶內(nèi)相位噪聲,抖動(dòng)可低至<50 fs。適用于高速ADC/DAC、光通信等對(duì)時(shí)鐘抖動(dòng)極度敏感的應(yīng)用。需外接PFD與本振(LO),系統(tǒng)復(fù)雜度略高,但性能接近儀表級(jí)。

直接數(shù)字頻率合成器(DDS):基于NCO+DAC架構(gòu),頻率切換速度達(dá)ns級(jí),頻率/相位分辨率極高(<1 μHz),輸出失真低。但輸出頻譜受奈奎斯特限制(通常< f_clk/2),且雜散性能依賴(lài)DAC線性度。適合信號(hào)發(fā)生器、雷達(dá)波形合成、測(cè)試設(shè)備等需高捷變與高分辨率的場(chǎng)景。

低相噪+固定頻率 → XO/VCXO

寬調(diào)諧+中等相噪 → 集成PLL+VCO

超低抖動(dòng)時(shí)鐘 → 轉(zhuǎn)換環(huán)路

快速跳頻+精細(xì)調(diào)諧 → DDS

成本敏感+中等性能 → 分立PLL+VCO方案

工程師應(yīng)根據(jù)系統(tǒng)對(duì)頻率范圍、相噪、切換速度、功耗及成本的優(yōu)先級(jí),權(quán)衡上述方案。隨著集成度提升,單芯片頻率合成器正成為主流,但理解底層原理仍是優(yōu)化系統(tǒng)性能的關(guān)鍵。