現(xiàn)貨庫存,2小時發(fā)貨,提供寄樣和解決方案

熱搜關鍵詞:

在當今數(shù)字時代,中央處理器(CPU)已經(jīng)成為計算機系統(tǒng)中最關鍵的組成部分之一。CPU的作用類似于人類大腦的中樞,負責執(zhí)行各種計算任務和控制計算機的各個部件。而CPU內(nèi)部的電子元器件是實現(xiàn)這些復雜運算的關鍵。電子元器件現(xiàn)貨供應商-中芯巨能將為您介紹電子元器件如何實現(xiàn)CPU的運算,包括CPU的基本結(jié)構以及各種電子元器件在其中的作用。

CPU通常由兩個主要部分組成:控制單元(CU)和算術邏輯單元(ALU)。控制單元負責從存儲器中獲取指令,并解釋執(zhí)行這些指令,控制數(shù)據(jù)在CPU內(nèi)部的流動以及與外部設備的通信。而算術邏輯單元則負責執(zhí)行各種算術和邏輯運算,比如加法、減法、乘法、除法以及邏輯運算(如與、或、非等)。

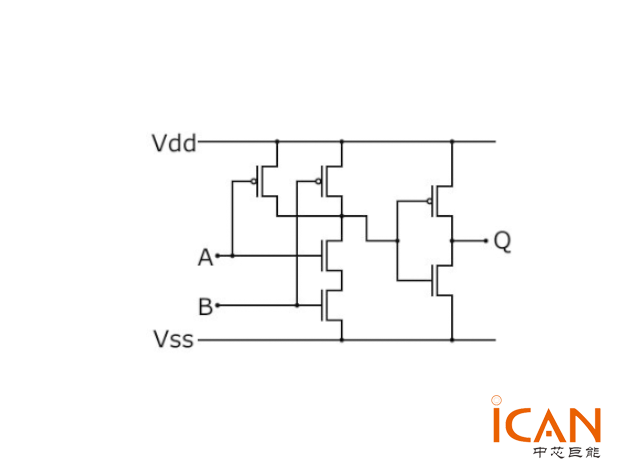

例如:與門電路運算:

與門電路是指只有在一件事情的所有條件都具備時,事情才會發(fā)生。

下面是由MOS管組成的電路圖。A和B作為輸入,Q作為輸出。

例如A輸入低電平、B輸出高電平,那么Q就會輸出低電平;轉(zhuǎn)換為二進制就是A輸入0、B輸出1,那么Q就會輸出0,對應的C語言運算表達式為0&&1=0。

1. 晶體管(Transistors):晶體管是CPU中最基本的電子元器件之一,它們用于構建邏輯門和存儲元件。邏輯門是實現(xiàn)各種邏輯運算的基礎,而存儲元件則用于存儲數(shù)據(jù)和指令。晶體管的開關特性使得它們可以實現(xiàn)邏輯門的功能,從而執(zhí)行各種運算。

2. 集成電路(Integrated Circuits,ICs):集成電路是將大量的晶體管和其他電子元器件集成到一個芯片上的技術。CPU中的各個功能模塊,如ALU、寄存器、控制器等,通常都是由集成電路實現(xiàn)的。集成電路的高集成度和小尺寸使得CPU能夠在較小的空間內(nèi)集成大量的功能模塊,從而提高了計算機系統(tǒng)的性能和效率。

3. 時鐘(Clock):時鐘是CPU中用于同步各個部件操作的關鍵元器件。時鐘發(fā)出的脈沖信號用于同步CPU中的各個功能模塊的操作,確保它們按照正確的順序和時序執(zhí)行。時鐘的頻率決定了CPU的工作速度,通常以赫茲(Hz)為單位表示,例如1 GHz表示每秒鐘發(fā)出10億次脈沖信號。

4. 寄存器(Registers):寄存器是CPU內(nèi)部用于存儲臨時數(shù)據(jù)和指令的高速存儲器件。CPU中包含多個不同類型的寄存器,如通用寄存器、指令寄存器、程序計數(shù)器等。寄存器的快速訪問速度使得CPU能夠快速執(zhí)行各種計算任務,并且可以暫時存儲計算結(jié)果和中間數(shù)據(jù)。

5. 緩存(Cache):緩存是CPU與主存儲器之間的高速臨時存儲器,用于加速對數(shù)據(jù)和指令的訪問。CPU中的緩存通常分為多級,包括一級緩存(L1 Cache)、二級緩存(L2 Cache)和三級緩存(L3 Cache)等。緩存的存在可以減少CPU對主存儲器的訪問次數(shù),從而提高數(shù)據(jù)訪問速度和系統(tǒng)整體性能。

在CPU中,運算的過程通常分為以下幾個步驟:

1. 取指令(Fetch):控制單元從主存儲器中獲取下一條要執(zhí)行的指令,并將其存儲到指令寄存器中。

2. 解碼指令(Decode):控制單元解析指令的操作碼,并確定需要執(zhí)行的操作類型。

3. 執(zhí)行指令(Execute):根據(jù)解碼的結(jié)果,控制單元將指令發(fā)送到算術邏輯單元或其他功能單元中執(zhí)行實際的計算或操作。

4. 訪存(Memory Access):如果指令涉及到內(nèi)存操作(如讀取或?qū)懭霐?shù)據(jù)),CPU將通過地址總線和數(shù)據(jù)總線與主存儲器進行通信,從而完成數(shù)據(jù)的讀寫操作。

5. 寫回(Write Back):如果指令執(zhí)行產(chǎn)生了結(jié)果,CPU將結(jié)果寫回到相應的寄存器或內(nèi)存位置中。

這些步驟通過時鐘信號的同步來實現(xiàn),確保各個功能模塊按照正確的順序和時序執(zhí)行。通過不斷重復這些步驟,CPU能夠?qū)崿F(xiàn)各種復雜的計算任務和邏輯操作。

電子元器件的不斷進步和發(fā)展使得現(xiàn)代CPU能夠具備強大的計算能力和高效的運算速度。CPU內(nèi)部的各種電子元器件相互配合,通過精密的控制和協(xié)調(diào)實現(xiàn)各種復雜的運算任務,為計算機系統(tǒng)的高性能和高效率提供了堅實的基礎。隨著技術的不斷進步,相信未來CPU的運算能力將會繼續(xù)得到提升,為人類帶來更多的科學、工程和生活上的便利。如需采購電子元器件、申請樣片測試、BOM配單等需求,請加客服微信:13310830171。